When it comes to machine vision cameras and systems, the core competency engineers usually use relies on configuring the core camera features to provide the best possible image while meeting size, weight, power budget and other requirements. In addition, successfully streaming the image from the camera to the host can be time consuming. Since leading edge vision transport layer standards (such as GigE, USB3 and CoaXPress) are complex and evolving, months of work by experienced protocol engineers are required to design the interface.

Several manufacturers of machine vision cameras such as Ozray, Crevis and Sick try to answer this challenge by investing in transport layer interfaces in the form of intellectual property (IP) which is offered ready to incorporate into field programmable gate arrays (FPGAs) along with other camera features. June Hwang, Chief Executive Officer of Crevis stated: “The biggest advantage of using IP cores is that we can create a reliable standard transmission interface in a fraction of the time previously required”.

“Use of IP Cores enables us to develop more cameras at the same time while reducing time to market,” Keith Ahn, Executive Director and Chief Technology Officer at Ozray

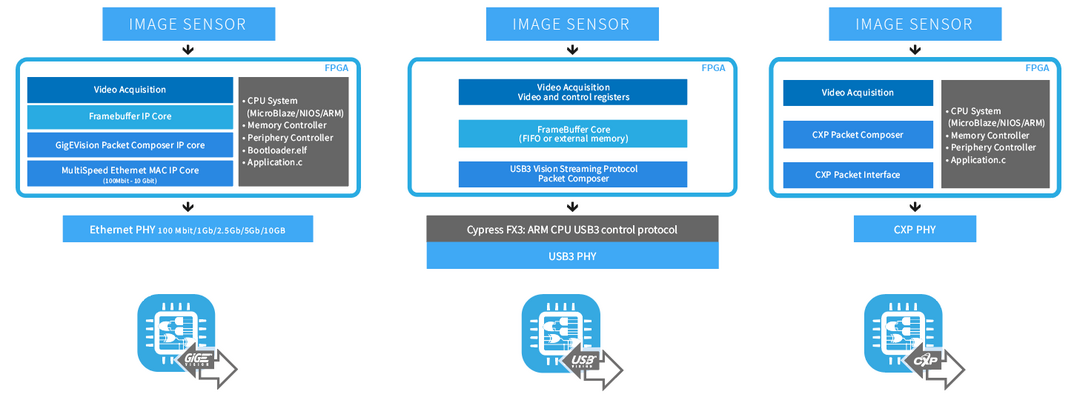

The emergence of machine vision transport layer IP cores reduces the time required to develop camera-host interfaces. For instance, Sensor to Image (S2I), a unit of Euresys, provides IP cores that meet the latest CXP, GigE Vision and USB3 Vision interface standards. These IP cores secure the interoperability of the camera and host while ensuring compliance with the latest version of the interface layer. S2I’s Vision Standard IP Cores solutions are delivered as a working reference design along with FPGA IP cores that have been fully tested against a wide range of popular frame grabbers and image acquisition libraries. They are compatible with Xilinx 7, Intel/Altera Cyclone V and more recent devices.

The top-level design, consisting of the interface between external hardware such as the image sensor and transport layer PHY, is delivered as VHDL source code that can be adapted to custom hardware beyond the leading FPGA platforms supported by IP cores. The Video Acquisition Module of the reference design simulates a camera with a test pattern generator. This module is delivered as VHDL source code which is replaced by a sensor interface and pixel processing logic in the camera design. An FPGA integrated CPU (either MicroBlaze, NIOS or ARM) is used for several non-time-critical control and configuration tasks on the Vision Standard IP Cores. This software is written in C and can be extended by the customer.

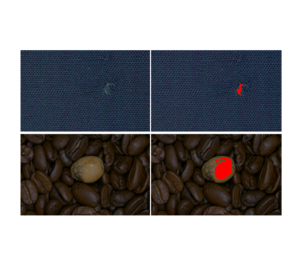

Compact, the IP cores leave plenty of room for additional vision functionality

“By reusing IP cores, machine vision companies can focus on how to make the best image while maintaining full freedom to use any hardware needed to meet size, weight and power budget issues,” said Jean Caron, Vice President Sales and Support, EMEA for Euresys. “We work closely with the CoaXPress, USB3 Vision and GigE Vision committees to ensure that our IP cores comply with the latest revisions of the standards,” said Matthias Schaffland, IP Product Specialist at S2I. S2I has recently introduced an IMX Pregius IP core offering an interface to Sony Pregius Sub-LVDS image sensors. Moreover, the company will soon introduce an interface to MIPI sensors primarily used in embedded vision systems and mobile devices. S2I provides a volume license well suited for companies with a large product line as well as a single-piece license which is a better option for companies with smaller lines. “IP Cores enable machine vision companies to build FPGA-based products using the GigE Vision, USB3 Vision, and CoaXPress standards, delivering the highest possible performance in a small footprint while minimizing development time,” Schaffland concluded.